Projet Pacman : Différence entre versions

(→Transmission d’un octet) |

(→Transmission d’un octet) |

||

| Ligne 94 : | Ligne 94 : | ||

| − | [[Fichier: | + | [[Fichier:Transss.png|cadre|gauche]] |

| + | |||

| + | |||

Dans cet exemple : | Dans cet exemple : | ||

-SCL : Horloge imposée par le maître. | -SCL : Horloge imposée par le maître. | ||

Version du 4 octobre 2013 à 17:09

Sommaire

La manette Nunchuk

Qu'est ce que le Nunchuk ?

Il s'agit de l'extension de base de la Wiimote,elle sert notamment dans la plupart des jeux. elle doit son nom Nunchuck" à sa ressemblance avec un nunchaku.

Relié à la Wiimote par le biais d'une connexion filaire, il comprend un stick analogique(joystick) deux axes, un accéléromètre trois axes et deux boutons tout ou rien "C" et "Z". Fourni dans la boîte de la Wee à l'achat, il est équipé d’accéléromètres pour la reconnaissance des mouvements, mais n'est ni équipé de haut- parleur, ni de moteur de vibration.

Le Protocole Utilisé: I²C

Présentation

Historique

Le bus I2C (Inter Integrated Circuit) a été développé au début des années 80 par Philips semi-conductors pour permettre de relier facilement à un microprocesseur les différents circuits d'un téléviseur moderne.

Caractéristiques

- Deux lignes uniquement (SDA et SCL) + Masse

- Une adresse unique pour chaque périphérique

- Bus multi-maître, détection des collisions et arbitrage

- Bus série, 8 bits, bidirectionnel à 100 kbps (standard mode), 400 kbps (fast mode), 3,2 Mbps (high-speed-mode)

- Filtrage intégré : réjection des pics parasites

- Nombre de circuits uniquement limité par la capacitance maximale du bus : 400 pF

Principe

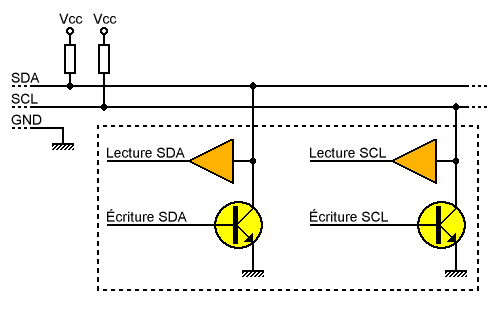

Le premier fil, SDA (Signal DAta), est utilisé pour transmettre les données. L'autre fil, SCL (Signal CLock) est utilisé pour transmettre un signal d'horloge synchrone (signal qui indique le rythme d'évolution de la ligne SDA). Les tensions associées aux niveaux logiques vont dépendre de la technologie des circuits en présence (CMOS, TTL). Il faudra que tous les circuits connectés au bus I²C utilisent les mêmes potentiels pour définir les niveaux haut et bas. En définitive, cela implique que tous les composants connectés à un même bus soient alimentés de façon identique. Cela ne signifie pas que les composants doivent utiliser la même source pour s'alimenter ; il suffit que la tension d'alimentation soit à la même valeur pour tous les composants, le fil de masse permettant d'unifier les références. Il reste maintenant un problème crucial. Comment permettre à plusieurs circuits logiques de connecter leurs sorties ensemble, sachant que certains circuits voudront imposer un niveau haut tandis que d'autres voudront imposer un niveau bas ? La réponse est connue depuis longtemps. Il faut utiliser des sorties à collecteur ouvert (ou à drain ouvert pour des circuits CMOS). Le niveau résultant sur la ligne est alors une fonction « ET » de toutes les sorties connectées.

Les résistances de rappel au potentiel VCC permettent aux signaux SDA et SCL d'être à 1 si toutes les sorties à, collecteurs ouverts sont aussi au niveau 1 (résultat de la fonction « ET »). Si une ou plusieurs sorties tentent d'imposer un niveau bas sur une ligne, le ou les transistors associés vont conduire, ce qui entraîne un niveau bas sur la ligne correspondante (ce qui est conforme au résultat de la fonction « ET »).

En ce qui concerne la lecture des signaux SDA et SCL, cela ne pose pas de problème. Les signaux peuvent être lus en permanence sans risque d'interférer sur le niveau de la ligne.

Au repos, tous les circuits connectes doivent imposer un niveau haut sur leurs sorties respectives. Si les lignes SDA et SCL sont au niveau haut dans ces conditions, cela signifie qu'aucun circuit ne tente de prendre le contrôle du bus. Si une des lignes SDA ou SCL passe à un niveau bas dans les mêmes conditions, c'est qu'un des circuits désire prendre le contrôle du bus. Mais il peut aussi y avoir deux circuits qui tentent de prendre le contrôle du bus en même temps (ou à quelques nanosecondes d'écart près). Il faut donc mettre en place un protocole pour gérer les conflits possibles.

Protocole

La prise de contrôle du bus

Pour prendre le contrôle du bus, il faut que celui-ci soit au repos (SDA et SCL à '1'). Pour transmettre des données sur le bus, il faut donc surveiller deux conditions particulières :

- La condition de départ. (SDA passe à '0' alors que SCL reste à '1')

- La condition d'arrêt. (SDA passe à '1' alors que SCL reste à '1')

Lorsqu'un circuit, après avoir vérifié que le bus est libre, prend le contrôle de celui-ci, il en devient le maître. C'est toujours le maître qui génère le signal d'horloge.

Exemple de condition de départ et d'arrêt :

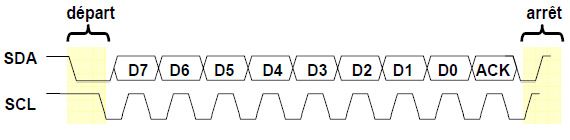

Transmission d’un octet

Le maître transmet le bit de poids fort D7 sur SDA. Il valide la donnée en apliqueant un niveau ‘1’ sur SCL. Lorsque SCL retombe à ‘0’, il poursuit avec D6, etc. jusqu‘à ce que l’octet complet soit transmis. Il envoie le bit ACK à ‘1’ en scrutant l’état réel de SDA. L’esclave doit imposer un niveau ‘0’ pour signaler que la transmission s’est d éroulée correctement. Le maître voit le ‘0’ (colelcteur ouvert) et peut passer à la suite.

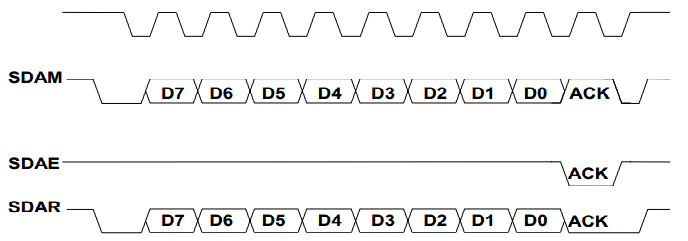

Dans cet exemple :

-SCL : Horloge imposée par le maître.

-SDAM : Niveaux de SDA imposés par le maître.

-SDAE : Niveaux de SDA imposés par l'esclave.

-SDAR : Niveaux de SDA réels résultants.