Cours:SaeCpld : Différence entre versions

(→obtenir la position du rotor) |

|||

| (28 révisions intermédiaires par 2 utilisateurs non affichées) | |||

| Ligne 16 : | Ligne 16 : | ||

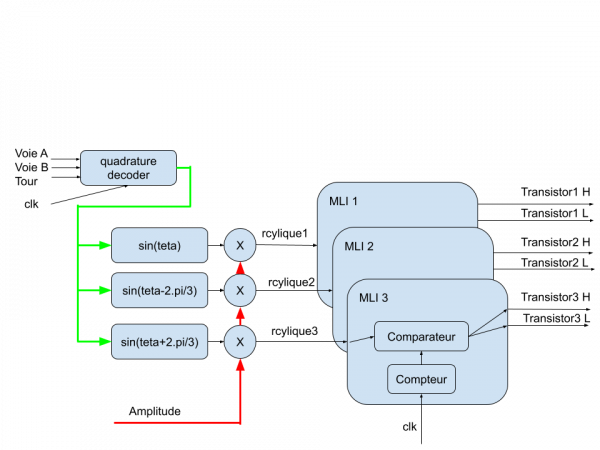

Vous allez réaliser la commande d'un moteur brushless (moteur synchrone à aimant permanent) | Vous allez réaliser la commande d'un moteur brushless (moteur synchrone à aimant permanent) | ||

| + | |||

| + | [[Image:SaeMoteurSynchroneSchemaFonctionnel.png|600px]] | ||

=Tâches à réaliser= | =Tâches à réaliser= | ||

==obtenir la position du rotor== | ==obtenir la position du rotor== | ||

| + | |||

| + | composant [[Media:Osram_AS5145.pdf|AS5145 Osram]] | ||

| + | |||

| + | ATTENTION : | ||

| + | *mettre l'entrée CS à 0 | ||

| + | *alimenter en 3.3v !! | ||

| + | **relier la broche 5v au 3.3V | ||

| + | **relier la broche 3v au 3.3V | ||

==interface utilisateur== | ==interface utilisateur== | ||

| + | On cherche à mettre en place une interface utilisateur pour faciliter le développement de l'application. Pour cela, on dispose sur la carte DE10-Lite : | ||

| + | * des 6 afficheurs 7 segments et des 10 leds de la carte DE10 pour la visualisation | ||

| + | * des 10 switch et des 2 boutons poussoirs pour positionner des entrées | ||

| + | |||

| + | Une autre approche possible est la mise en oeuvre d'un afficheur à cristaux liquides ( Liquid Crystal Display) 2 lignes de 20 caractères. | ||

==génération des PWMs== | ==génération des PWMs== | ||

| − | On utilisera dans un 1er temps | + | On utilisera dans un 1er temps la carte DE10-Lite exploitée lors des TPs XR3.16. Le pdf de la documentation de la carte est fournie en ressources ci-dessous pour disposer des brochages des différents matériels ( switch, boutons poussoir, leds, afficheurs 7 segments, connecteur IDE40, empreinte shield arduino ... ) |

| + | |||

===module PWM=== | ===module PWM=== | ||

| Ligne 31 : | Ligne 47 : | ||

*en entrées: | *en entrées: | ||

**clk : horloge à 50MHz | **clk : horloge à 50MHz | ||

| − | **rcyclique : integer 0 à | + | **rcyclique : integer 0 à 2047 |

**enable : bit | **enable : bit | ||

*2 sorties : | *2 sorties : | ||

| Ligne 38 : | Ligne 54 : | ||

*description du fonctionnement | *description du fonctionnement | ||

**les changements d'état des sorties se feront uniquement sur un front montant de l'horloge | **les changements d'état des sorties se feront uniquement sur un front montant de l'horloge | ||

| − | **un compteur modulo | + | **un compteur modulo 2048 s'incrémente sur chaque front d'horloge |

**si enable=0 alors les sorties sont à 0 | **si enable=0 alors les sorties sont à 0 | ||

**si enable=1 alors : | **si enable=1 alors : | ||

| Ligne 47 : | Ligne 63 : | ||

{{Question|vérifier le fonctionnement en utilisant des switch pour modifier le rapport cyclique}} | {{Question|vérifier le fonctionnement en utilisant des switch pour modifier le rapport cyclique}} | ||

| + | ===Incrémentation automatique du rapport cyclique=== | ||

| + | |||

| + | On ajoute un module qui incrémentera régulièrement la valeur du rapport cyclique. | ||

| + | |||

| + | créer un module : | ||

| + | *avec 1 entrée d'horloge à 50MHz | ||

| + | *1 sortie de type entier entre 0 et 2047 | ||

| + | *incrémente le rapport cyclique tous les 50000 fronts d'horloge | ||

| + | |||

| + | {{Question|ajouter un filtre passe bas sur votre/vos sorties et vérifier le bon fonctionnement}} | ||

| + | |||

| + | === Modification automatique du rapport cyclique : via valeurs lues en mémoire === | ||

| + | |||

| + | On s'appuiera sur le CM et les TPs de XR3.16 pour mener à bien cette partie description/utilisation de mémoire. | ||

| + | |||

| + | * Mémoire : | ||

| + | ** Créer un module mémoire ROM à 1 Port de 128 mots de 10 bits ( une LPM_ROM depuis l'ip_catalog ou un type array en VHDL ) | ||

| + | ** Initialiser le contenu de la mémoire (fichier .mif ou initialisation du tableau en VHDL) avec des valeurs régulièrement croissantes puis décroissantes entre 0 et 1023, l'enchaînement de ces valeurs numériques décrivant ainsi l'équivalent d'un signal triangulaire. | ||

| + | |||

| + | * Compteur : réaliser un compteur modulo 128 s'incrémentant de 1 tous les 50000 fronts d'horloge ( horloge à 50MHz) . On pourra éventuellement décomposer cela en 2 fonctions logiques | ||

| + | ** préparer un signal d'horloge à 1KHz ( 1 front montant tous les 50000 fronts d'horloge de l'entrée à 50MHz ) | ||

| + | ** réaliser un compteur modulo 128 à cette fréquence de 1KHz dont on utilisera la valeur pour adresser la mémoire. | ||

| + | |||

| + | * Test : implanter les 3 modules précédents | ||

| + | ** compteur modulo 128 à 1Khz | ||

| + | ** mémoire 128 mots de 10 bits adressée par le compteur | ||

| + | ** module PWM dont le rapport cyclique ( sur 10 bits) est issu de la lecture de la mémoire | ||

| + | |||

| + | {{Question|ajouter un filtre passe bas sur votre/vos sorties et vérifier le bon fonctionnement}} | ||

| + | |||

| + | |||

| + | === Modification/Evolution sinusoïdale du rapport cyclique === | ||

| + | |||

| + | * Préparation | ||

| + | ** Exploiter un tableur (excel / Libreoffice ) pour calculer les valeurs de ( 1 + sin(x) ). Avec x prenant 128 valeurs régulièrement réparties dans les 360 degrés d'une période de sinus. | ||

| + | ** Compléter votre tableau par une colonne calculant la partie entière de 512 * ( 1+ sin(x) ). | ||

| + | ** Vérifier que vos valeurs sont bien situées dans la plage [0;2]. Le cas échéant, biaiser la valeur 0 à 1 et la valeur 2 à 1,99 . Cette modification a pour but d'éviter de produire une PWM totalement à 0 ou totalement à 1. | ||

| + | |||

| + | * Test : reprendre le test précédent avec la mémoire initialisée avec les valeurs de cette dernière colonne calculée dans votre tableur. | ||

| + | |||

| + | |||

| + | {{Question|ajouter un filtre passe bas sur votre/vos sorties et vérifier le bon fonctionnement}} | ||

=Liens/Ressources= | =Liens/Ressources= | ||

| + | *[[Media:DE10-Lite_User_Manual.pdf]] | ||

| + | *[[Media:Vcnt2020.zip]] | ||

| + | *[[Media:CarteFourcheOptique.zip]] | ||

| + | *[[Media:CarteMos.zip]] | ||

| + | *[[Media:ressource_lcd2x20.zip]] | ||

| + | *[[Media:binbcd5.zip]] | ||

| + | |||

| + | *animations moteurs | ||

| + | **https://www.dailymotion.com/video/xmezeb | ||

| + | **https://christophehaouy.wixsite.com/electrotechnique-exp/moteurs-electriques | ||

| + | **https://sitelec.org/cours/abati/synch.htm | ||

| + | **https://www.youtube.com/watch?v=bpwJBGpEi0Q | ||

| + | **https://www.geogebra.org/m/ptdxJezR | ||

| + | |||

| + | =Exemples= | ||

| + | |||

| + | <source lang=vhdl> | ||

| + | library IEEE; | ||

| + | use IEEE.std_logic_1164.all; | ||

| + | use IEEE.std_logic_unsigned.all; | ||

| + | |||

| + | entity tabSinus is | ||

| + | port (clk :in std_logic; | ||

| + | angle : in integer range 0 to 4; | ||

| + | sin : out integer range 0 to 7 | ||

| + | ); | ||

| + | end tabSinus; | ||

| + | |||

| + | architecture Behavioral of tabSinus is | ||

| + | type memory_type is array (0 to 4) of integer range 0 to 7; | ||

| + | |||

| + | signal tabsin : memory_type :=(0, 2, 4, 6, 7); | ||

| + | |||

| + | begin | ||

| + | |||

| + | process(clk) | ||

| + | begin | ||

| + | --to check the rising edge of the clock signal | ||

| + | if(rising_edge(clk)) then | ||

| + | sin <= tabsin(angle); | ||

| + | end if; | ||

| + | end process; | ||

| + | end Behavioral; | ||

| + | </source> | ||

=Historique= | =Historique= | ||

*[[Cours:SaeCpldHistorique]] | *[[Cours:SaeCpldHistorique]] | ||

Version actuelle datée du 6 janvier 2026 à 13:25

Sommaire

Modalité d'évaluation

Organisation des travaux

- Le travail sera mené par trinôme. Vous devrez organiser vos travaux de manière à ce que chacun soit actif pour faire avancer le projet

- Il y aura une partie individuelle

- puis 1 travail de regroupement du travail

Calendrier indicatif

Présentation du projet

Vous allez réaliser la commande d'un moteur brushless (moteur synchrone à aimant permanent)

Tâches à réaliser

obtenir la position du rotor

composant AS5145 Osram

ATTENTION :

- mettre l'entrée CS à 0

- alimenter en 3.3v !!

- relier la broche 5v au 3.3V

- relier la broche 3v au 3.3V

interface utilisateur

On cherche à mettre en place une interface utilisateur pour faciliter le développement de l'application. Pour cela, on dispose sur la carte DE10-Lite :

- des 6 afficheurs 7 segments et des 10 leds de la carte DE10 pour la visualisation

- des 10 switch et des 2 boutons poussoirs pour positionner des entrées

Une autre approche possible est la mise en oeuvre d'un afficheur à cristaux liquides ( Liquid Crystal Display) 2 lignes de 20 caractères.

génération des PWMs

On utilisera dans un 1er temps la carte DE10-Lite exploitée lors des TPs XR3.16. Le pdf de la documentation de la carte est fournie en ressources ci-dessous pour disposer des brochages des différents matériels ( switch, boutons poussoir, leds, afficheurs 7 segments, connecteur IDE40, empreinte shield arduino ... )

module PWM

créer un module PWM qui aura :

- en entrées:

- clk : horloge à 50MHz

- rcyclique : integer 0 à 2047

- enable : bit

- 2 sorties :

- tH : bit qui pilotera le transistor du haut du 1/2 pont

- tL : bit qui pilotera le transistor du bas du 1/2 pont

- description du fonctionnement

- les changements d'état des sorties se feront uniquement sur un front montant de l'horloge

- un compteur modulo 2048 s'incrémente sur chaque front d'horloge

- si enable=0 alors les sorties sont à 0

- si enable=1 alors :

- si compteur<rcylique tH=1 et tL=0

- si compteur>rcyclique tH=0 et tL=1

![]() vérifier le fonctionnement en utilisant des switch pour modifier le rapport cyclique

vérifier le fonctionnement en utilisant des switch pour modifier le rapport cyclique

Incrémentation automatique du rapport cyclique

On ajoute un module qui incrémentera régulièrement la valeur du rapport cyclique.

créer un module :

- avec 1 entrée d'horloge à 50MHz

- 1 sortie de type entier entre 0 et 2047

- incrémente le rapport cyclique tous les 50000 fronts d'horloge

![]() ajouter un filtre passe bas sur votre/vos sorties et vérifier le bon fonctionnement

ajouter un filtre passe bas sur votre/vos sorties et vérifier le bon fonctionnement

Modification automatique du rapport cyclique : via valeurs lues en mémoire

On s'appuiera sur le CM et les TPs de XR3.16 pour mener à bien cette partie description/utilisation de mémoire.

- Mémoire :

- Créer un module mémoire ROM à 1 Port de 128 mots de 10 bits ( une LPM_ROM depuis l'ip_catalog ou un type array en VHDL )

- Initialiser le contenu de la mémoire (fichier .mif ou initialisation du tableau en VHDL) avec des valeurs régulièrement croissantes puis décroissantes entre 0 et 1023, l'enchaînement de ces valeurs numériques décrivant ainsi l'équivalent d'un signal triangulaire.

- Compteur : réaliser un compteur modulo 128 s'incrémentant de 1 tous les 50000 fronts d'horloge ( horloge à 50MHz) . On pourra éventuellement décomposer cela en 2 fonctions logiques

- préparer un signal d'horloge à 1KHz ( 1 front montant tous les 50000 fronts d'horloge de l'entrée à 50MHz )

- réaliser un compteur modulo 128 à cette fréquence de 1KHz dont on utilisera la valeur pour adresser la mémoire.

- Test : implanter les 3 modules précédents

- compteur modulo 128 à 1Khz

- mémoire 128 mots de 10 bits adressée par le compteur

- module PWM dont le rapport cyclique ( sur 10 bits) est issu de la lecture de la mémoire

![]() ajouter un filtre passe bas sur votre/vos sorties et vérifier le bon fonctionnement

ajouter un filtre passe bas sur votre/vos sorties et vérifier le bon fonctionnement

Modification/Evolution sinusoïdale du rapport cyclique

- Préparation

- Exploiter un tableur (excel / Libreoffice ) pour calculer les valeurs de ( 1 + sin(x) ). Avec x prenant 128 valeurs régulièrement réparties dans les 360 degrés d'une période de sinus.

- Compléter votre tableau par une colonne calculant la partie entière de 512 * ( 1+ sin(x) ).

- Vérifier que vos valeurs sont bien situées dans la plage [0;2]. Le cas échéant, biaiser la valeur 0 à 1 et la valeur 2 à 1,99 . Cette modification a pour but d'éviter de produire une PWM totalement à 0 ou totalement à 1.

- Test : reprendre le test précédent avec la mémoire initialisée avec les valeurs de cette dernière colonne calculée dans votre tableur.

![]() ajouter un filtre passe bas sur votre/vos sorties et vérifier le bon fonctionnement

ajouter un filtre passe bas sur votre/vos sorties et vérifier le bon fonctionnement

Liens/Ressources

- Media:DE10-Lite_User_Manual.pdf

- Media:Vcnt2020.zip

- Media:CarteFourcheOptique.zip

- Media:CarteMos.zip

- Media:ressource_lcd2x20.zip

- Media:binbcd5.zip

- animations moteurs

Exemples

library IEEE;

use IEEE.std_logic_1164.all;

use IEEE.std_logic_unsigned.all;

entity tabSinus is

port (clk :in std_logic;

angle : in integer range 0 to 4;

sin : out integer range 0 to 7

);

end tabSinus;

architecture Behavioral of tabSinus is

type memory_type is array (0 to 4) of integer range 0 to 7;

signal tabsin : memory_type :=(0, 2, 4, 6, 7);

begin

process(clk)

begin

--to check the rising edge of the clock signal

if(rising_edge(clk)) then

sin <= tabsin(angle);

end if;

end process;

end Behavioral;