Cours:TP M1102 TP 3 Corr : Différence entre versions

m (→Question 2) |

m (→Question 2) |

||

| Ligne 190 : | Ligne 190 : | ||

END arch; | END arch; | ||

</source> | </source> | ||

| + | ==Exercice 2== | ||

| + | ==Exercice 3== | ||

Version du 25 septembre 2020 à 15:59

TP 3

Exercice 1

Question 1

La table de vérité donnée dans wikipédia est :

| A | B | Cin | S | Cout |

|---|---|---|---|---|

| 0 | 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 1 | 0 |

| 0 | 1 | 0 | 1 | 0 |

| 0 | 1 | 1 | 0 | 1 |

| 1 | 0 | 0 | 1 | 0 |

| 1 | 0 | 1 | 0 | 1 |

| 1 | 1 | 0 | 0 | 1 |

| 1 | 1 | 1 | 1 | 1 |

Nous allons la modifier légèrement pour ses entrées et sorties : les 3 entrées sont regroupées et les 2 sorties sont aussi regroupées ensemble

- Table de vérité

Entrées Sorties e(2)=Cin e(1)=B e(0)=A S(1)=Cout S(0)=S 0 0 0 0 0 0 0 1 0 1 0 1 0 0 1 0 1 1 1 0 1 0 0 0 1 1 0 1 1 0 1 1 0 1 0 1 1 1 1 1

ATTENTION : Nous avons aussi volontairement changé l'ordre ses entrées et des sorties.Il est préférable d'avoir les sorties dans ce sens pour avoir le poids fort des deux bits de sortie à gauche. Pour les entrées c'est moins important.

Voici le fichier VHDL correspondant :

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

ENTITY add1bit IS PORT(

e : in std_logic_vector(2 downto 0); -- Cin, B, A

s : out std_logic_vector(1 downto 0)); -- Cout, S

END add1bit;

ARCHITECTURE arch of add1bit IS

BEGIN

with e select

S <= "00" when "000", --0+0+0=00

"01" when "001", --0+0+1=01

"01" when "010", --0+1+0=01

"10" when "011", --0+1+1=10

"01" when "100", --1+0+0=01

"10" when "101", --1+0+1=10

"10" when "110", --1+1+0=10

"11" when others;--1+1+1=11

END arch;

Question 2

Il faut déjà définir les entrées et sorties de notre problème, autrement dit définir l'entité. Parmi les diverses solutions possibles, nous allons choisir

library IEEE;

use IEEE.std_logic_1164.all;

--use IEEE.std_logic_arith.all;

--use IEEE.STD_LOGIC_UNSIGNED.all;

ENTITY add4 IS

PORT (A,B : IN STD_LOGIC_VECTOR(3 DOWNTO 0);

Cin : IN STD_LOGIC; --retenue entrée dans le schéma

S : OUT STD_LOGIC_VECTOR(4 DOWNTO 0)); --retenue en S(4)

END add4;

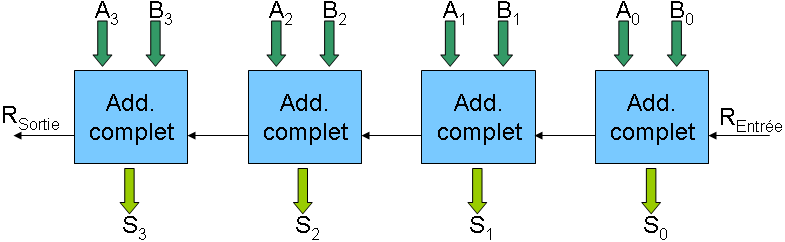

Si l'on compare au schéma de l'énoncé :

on impose ainsi les correspondances suivantes :

Schéma <-> VHDL

- REntrée <-> Cin

- A3 <-> A(3)

- A2 <-> A(2)

- A1 <-> A(1)

- A0 <-> A(0)

- B3 <-> B(3)

- B2 <-> B(2)

- B1 <-> B(1)

- B0 <-> B(0)

- RSortie <-> S(4)

- S3 <-> S(3)

- S2 <-> S(2)

- S1 <-> S(1)

- S0 <-> S(0)

Le programme VHDL devient :

library IEEE;

use IEEE.std_logic_1164.all;

--use IEEE.std_logic_arith.all;

--use IEEE.STD_LOGIC_UNSIGNED.all;

ENTITY add4 IS

PORT (A,B : IN STD_LOGIC_VECTOR(3 DOWNTO 0);

Cin : IN STD_LOGIC; --retenue entrée dans le schéma

S : OUT STD_LOGIC_VECTOR(4 DOWNTO 0)); --retenue en S(4)

END add4;

ARCHITECTURE arch_add4 of add4 IS

COMPONENT add1bit IS PORT(

e : in std_logic_vector(2 downto 0); -- Cin, B, A

s : out std_logic_vector(1 downto 0)); -- Cout, S

END COMPONENT add1bit;

SIGNAL R1, R2, R3 : std_logic; --fils internes non nommés dans le schéma : R1 à droite

BEGIN

i0: add1bit PORT MAP(

e(2) => Cin,

e(1) => B(0),

e(0) => A(0),

S(1) => R1,

S(0) => S(0)); --Il n'y a aucune ambiguité pour VHDL ici

i1: add1bit PORT MAP(

e(2) => R1,

e(1) => B(1),

e(0) => A(1),

S(1) => R2,

S(0) => S(1));

i2: add1bit PORT MAP(

e(2) => R2,

e(1) => B(2),

e(0) => A(2),

S(1) => R3,

S(0) => S(2));

i3: add1bit PORT MAP(

e(2) => R3,

e(1) => B(3),

e(0) => A(3),

S(1) => S(4),

S(0) => S(1));

END arch_add4

--******** Composant à câbler *********

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

ENTITY add1bit IS PORT(

e : in std_logic_vector(2 downto 0); -- Cin, B, A

s : out std_logic_vector(1 downto 0)); -- Cout, S

END add1bit;

ARCHITECTURE arch of add1bit IS

BEGIN

with e select

S <= "00" when "000", --0+0+0=00

"01" when "001", --0+0+1=01

"01" when "010", --0+1+0=01

"10" when "011", --0+1+1=10

"01" when "100", --1+0+0=01

"10" when "101", --1+0+1=10

"10" when "110", --1+1+0=10

"11" when others;--1+1+1=11

END arch;