Pilotage à partir du composant A4935 : Différence entre versions

(→Carte principale) |

(→Carte principale) |

||

| Ligne 14 : | Ligne 14 : | ||

Les entrées RESET(oublié sur notre carte à cause d'une erreur de notre part),CCEN, COAST, PWMH, PWML sont reliées chacune à des borniers de 3 pattes (deux des pattes sont reliées au seuil logique haut, et au seuil logique bas) afin de pouvoir affecter une valeur différente à ces entrées à l'aide d'un cavalier. | Les entrées RESET(oublié sur notre carte à cause d'une erreur de notre part),CCEN, COAST, PWMH, PWML sont reliées chacune à des borniers de 3 pattes (deux des pattes sont reliées au seuil logique haut, et au seuil logique bas) afin de pouvoir affecter une valeur différente à ces entrées à l'aide d'un cavalier. | ||

| + | |||

| + | Le VBB présent sur le schéma aurait également dû être relié à une alimentation (erreur de notre part). | ||

De plus, le composant A4935 n'étant pas placé de base de la librairie Eagle, il a fallut créer celui-ci. On a pu réutiliser un package déjà présent dans la librairie Eagle, celui-ci étant similaire à celui de la documentation (48-pin LQFP) | De plus, le composant A4935 n'étant pas placé de base de la librairie Eagle, il a fallut créer celui-ci. On a pu réutiliser un package déjà présent dans la librairie Eagle, celui-ci étant similaire à celui de la documentation (48-pin LQFP) | ||

Version du 15 janvier 2015 à 16:38

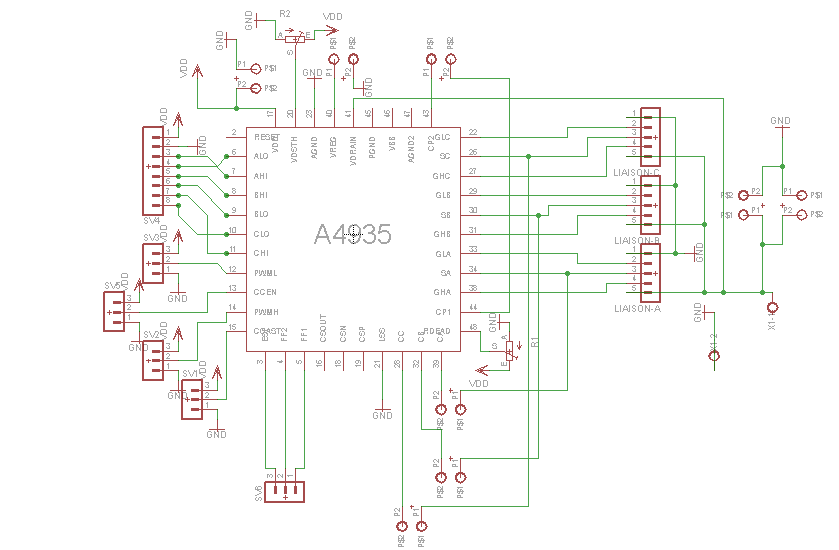

Le but est de fabriquer une carte permettant de tester le circuit-intégré A4935 ainsi que de déterminer les valeurs des différents composants qui lui seront associés.

Un schéma des blocs fonctionnels nous était fournis dans la documentation du composant.

Sommaire

Carte principale

Le micro-processeur A4935 sera placé dessus. Pour les différentes pattes qui devront avoir un seuil haut et un seuil bas, deux pattes seront reliées par un cavalier à chaque fois. Les condensateurs de découplage seront également placés là. Le condensateur CP sera remplacé par deux bornes afin de pouvoir faire différents test.

Les entrées xHI, xLO sont reliées à un bornier femelle afin de pouvoir choisir indépendamment les valeurs qui leur seront données (sur ce bornier sont également présents le seuil haut et bas pour les autres entrées).

Les entrées RESET(oublié sur notre carte à cause d'une erreur de notre part),CCEN, COAST, PWMH, PWML sont reliées chacune à des borniers de 3 pattes (deux des pattes sont reliées au seuil logique haut, et au seuil logique bas) afin de pouvoir affecter une valeur différente à ces entrées à l'aide d'un cavalier.

Le VBB présent sur le schéma aurait également dû être relié à une alimentation (erreur de notre part).

De plus, le composant A4935 n'étant pas placé de base de la librairie Eagle, il a fallut créer celui-ci. On a pu réutiliser un package déjà présent dans la librairie Eagle, celui-ci étant similaire à celui de la documentation (48-pin LQFP)

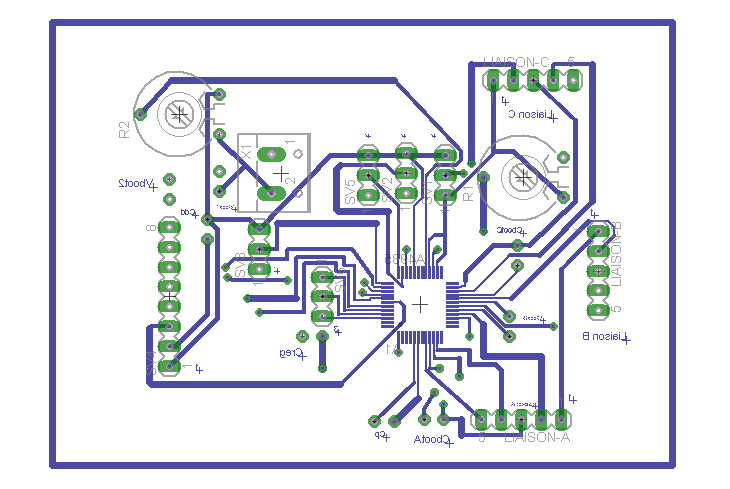

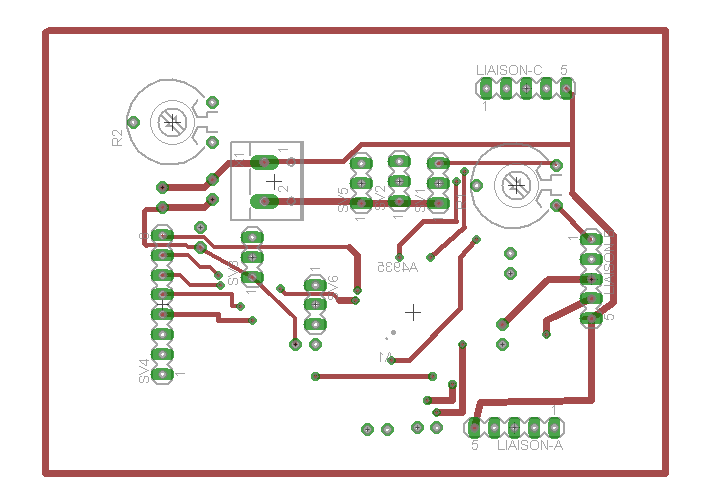

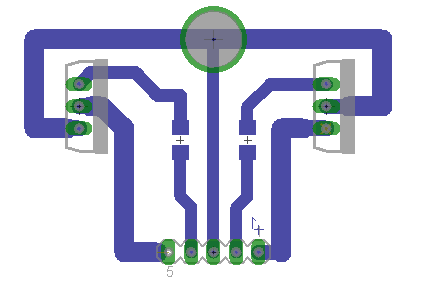

Routage Carte principale

Les pistes en sortie du composant A4935 sont les moins larges possibles afin de ne pas avoir de contact entre les différentes pattes. De plus, des détrompeurs sont présentes sur chacun des connecteurs, et chacun des noms de condensateur est noté afin de pouvoir les repérer plus simplement, sans forcément avoir le board à portée. Les connecteurs pour les cartes annexes sont tous les trois disposés sur trois côtés différents de la carte principale, au bord, afin de pouvoir connecter les annexes le plus simplement possible.

Le composant A4935 n'étant pas présent de base dans les librairies d'Eagle, nous avons du le créer pour l'occasion.

Media:ER_carte_test.brd Media:ER_carte_test.sch

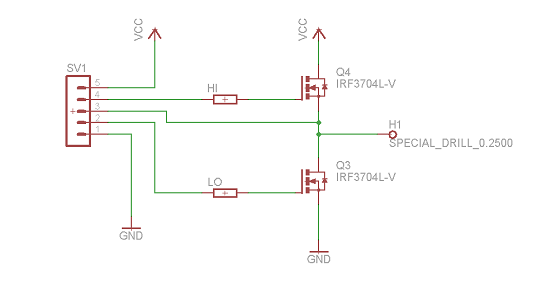

Carte annexe

Deux transistors C-MOS IRF2204 y seront positionnés. Cinq pattes seront reliées à la carte principale, à savoir GHA, SA, GLA, VCC ainsi que la masse.

Schéma et Board de la carte

Les pistes sont les plus larges possibles, 2.2 mm, puisqu'elles sont destinées à accueillir des grosses valeurs de courant. Deux détrompeurs sont présents au niveau du connecteur.

Media:Transiirf.brd Media:Transiirf.sch

Test des 3 cartes annexes

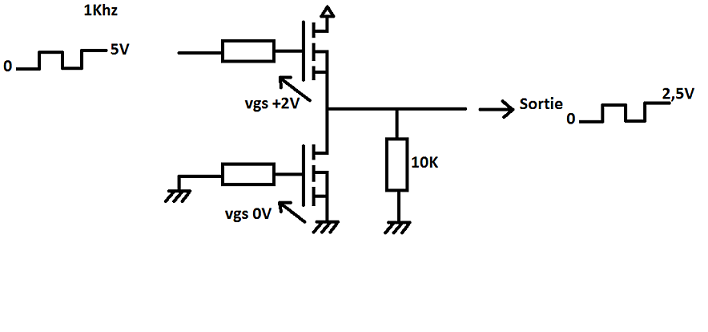

On effectue d'abord le test sur le transistor du haut, on rentre un signal carré (d'amplitude 0-5V et de fréquence 1kHz) et on met le transistor du bas à la masse. On observe en sortie un signal carré d'amplitude 0-2.5V, le transistor se bloque donc correctement. On effectue le même test pour les transistors haut des deux autres cartes.

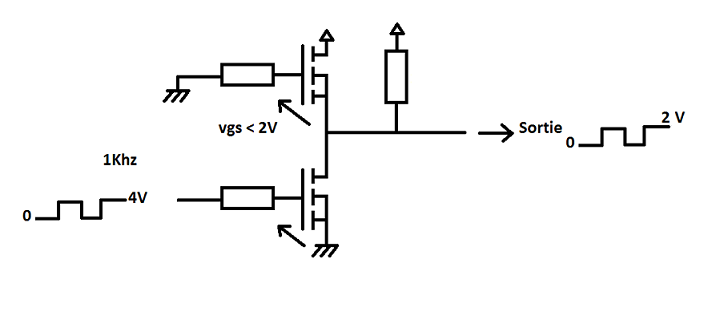

Pour le transistor du bas, on effectue la même manipulation mais avec un signal carré d'amplitude 0-4V et on met le transistor du haut à la masse. Ici aussi le transistor se bloque correctement, le signal de sortie est un signal carré d'amplitude 0-2V. On effectue le même test pour les transistors bas des deux autres cartes.