(non-PWM)

# 15.9 Register Description

#### 15.9.1 TCCR0A - Timer/Counter Control Register A

# Bits 7:6 - COM0A1:0: Compare Match Output A Mode

These bits control the Output Compare pin (OCDA) behavior. If one or both of the COMMA10 bits are set, the CODA output overrides the normal port functionality of the 10 pin it is connected to 1-thowever, note that the Data Direction Register (DOR) bit corresponding to the OCDA pin must be set in order to enable the output driver. When OCDA is connected to the pin, the function of the COMMA10 bits despend on the WGMID2 bit setting. Table 15-2 although the COMMA10 bit dependence on the COMMA10 bits despendence on the WGMID2 bit setting.

Table 15-2. Compare Output Mode, non-PWM Mode

| COM0A1 | COM0A0 | Description                               |

|--------|--------|-------------------------------------------|

| 0      | 0      | Normal port operation, OC0A disconnected. |

| 0      | 1      | Toggle OC0A on Compare Match              |

| 1      | 0      | Clear OC0A on Compare Match               |

| 1      | 1      | Set OC0A on Compare Match                 |

Table 15-3 shows the COM0A1:0 bit functionality when the WGM01:0 bits are set to fast PWM mode.

Table 15-3. Compare Output Mode, Fast PWM Mode

| rubic 10-0. | Compare Gutp                                                                                    | at mode, i ast i vim mode                                              |  |  |  |  |  |

|-------------|-------------------------------------------------------------------------------------------------|------------------------------------------------------------------------|--|--|--|--|--|

| COM0A1      | COM0A0                                                                                          | Description                                                            |  |  |  |  |  |

| 0           | 0                                                                                               | Normal port operation, OC0A disconnected.                              |  |  |  |  |  |

| 0           | 0 1 WGM02 = 0: Normal Port Operation, OC0A Disconnecte WGM02 = 1: Toggle OC0A on Compare Match. |                                                                        |  |  |  |  |  |

| 1           | 0                                                                                               | Clear OC0A on Compare Match, set OC0A at BOTTOM, (non-inverting mode). |  |  |  |  |  |

| 1           | 1                                                                                               | Set OCOA on Compare Match, clear OCOA at BOTTOM,<br>(inverting mode)   |  |  |  |  |  |

Note: 1. A special case occurs when OCR0A equals TOP and COM0A1 is set. In this case, the Compare Match is ignored, but the set or clear is done at BOTTOM. See "Fast PWM Mode" on page 99 for more details.

Table 15-4 shows the COM0A1:0 bit functionality when the WGM02:0 bits are set to phase correct PWM mode.

Table 15-4. Compare Output Mode, Phase Correct PWM Mode 1

| COM0A1 | COM0A0 | Description                                                                                      |  |  |  |  |

|--------|--------|--------------------------------------------------------------------------------------------------|--|--|--|--|

| 0      | 0      | Normal port operation, OC0A disconnected.                                                        |  |  |  |  |

| 0      | 1      | WGM02 = 0: Normal Port Operation, OC0A Disconnected.<br>WGM02 = 1: Toggle OC0A on Compare Match. |  |  |  |  |

| 1      | 0      | Clear OC0A on Compare Match when up-counting. Set OC0A on<br>Compare Match when down-counting.   |  |  |  |  |

| 1      | 1      | Set OC0A on Compare Match when up-counting. Clear OC0A on Compare Match when down-counting.      |  |  |  |  |

Note: 1. A special case occurs when OCR0A equals TOP and COM0A1 is set. In this case, the Compare Match is ignored, but the set or clear is done at TOP. See "Phase Correct PWM Mode" on page 125 for more details.

# Bits 5:4 - COM0B1:0: Compare Match Output B Mode

These bits control the Output Compare pin (OCDB) behavior. If one or both of the COMDB 10 bits are set, the COCB output overrides the normal port functionality of the 10 pin it is connected to thewever, note that the Data Direction Register (IDR) bit corresponding to the OCDB pin must be set in order to enable the output driver. When OCDB is connected to the pin, the function of the COMDB10 bits depends on the WGMX2D bit setting. Table 15-5 shows the COMDB10 bit functionality when the WGMX2D bits are set to a normal or OTE mode

#### Table 15-5. Compare Output Mode, non-PWM Mode

| COM0B1 | COM0B0 | Description                               |  |  |  |  |

|--------|--------|-------------------------------------------|--|--|--|--|

| 0      | 0      | Normal port operation, OC0B disconnected. |  |  |  |  |

| 0      | 1      | Toggle OC0B on Compare Match              |  |  |  |  |

| 1      | 0      | Clear OC0B on Compare Match               |  |  |  |  |

| 1      | 1      | Set OC0B on Compare Match                 |  |  |  |  |

Table 15-6 shows the COM0B1:0 bit functionality when the WGM02:0 bits are set to fast PWM mode.

Table 15-6. Compare Output Mode, Fast PWM Mode(1)

| COM0B1 | COM0B0 | Description                                                              |

|--------|--------|--------------------------------------------------------------------------|

| 0      | 0      | Normal port operation, OC0B disconnected.                                |

| 0      | 1      | Reserved                                                                 |

| 1      | 0      | Clear OC0B on Compare Match, set OC0B at BOTTOM,<br>(non-inverting mode) |

| 1      | 1      | Set OC0B on Compare Match, clear OC0B at BOTTOM,<br>(inverting mode).    |

Note: 1. A special case occurs when OCR0B equals TOP and COM0B1 is set. In this case, the Compare Match is ignored, but the set or clear is done at TOP. See "Fast PWM Mode" on page 99 for more details.

Table 15-7 shows the COM0B1:0 bit functionality when the WGM02:0 bits are set to phase correct PWM mode.

Table 15.7 Compare Output Made Diseas Correct DWM Made

| iubic ioir. | Compare Gutp | at mode, i hase confect i vim mode                                                             |

|-------------|--------------|------------------------------------------------------------------------------------------------|

| COM0B1      | COM0B0       | Description                                                                                    |

| 0           | 0            | Normal port operation, OC0B disconnected.                                                      |

| 0           | 1            | Reserved                                                                                       |

| 1           | 0            | Clear OC0B on Compare Match when up-counting. Set OC0B on<br>Compare Match when down-counting. |

| 1           | 1            | Set OC0B on Compare Match when up-counting. Clear OC0B on Compare Match when down-counting.    |

Note: 1 A special case occurs when OCR0B equals TOP and COM0R1 is set. In this case, the Compare Match is ignored, but the set or clear is done at TOP. See "Phase Correct PWM Mode" on page 100 for more details.

#### · Bits 3. 2 - Reserved

These bits are reserved bits in the ATmega48A/PA/88A/PA/168A/PA/328/P and will always read as zero.

#### . Bits 1:0 - WGM01:0: Waveform Generation Mode

Combined with the WGM02 bit found in the TCCR0B Register, these bits control the counting sequence of the counter, the source for maximum (TOP) counter value, and what type of waveform generation to be used, see Table 15-8. Modes of operation supported by the Timer/Counter unit are: Normal mode (counter), Clear Timer on Compare Match (CTC) mode, and two types of Pulse Width Modulation (PWM) modes (see "Modes of Operation" on page 98).

Table 15-8. Waveform Generation Mode Bit Description

| Mode | WGM02 | WGM01 | WGM00 | Timer/Counter<br>Mode of<br>Operation | ТОР  | Update of OCRx at | TOV Flag<br>Set on <sup>(1)(2)</sup> |  |

|------|-------|-------|-------|---------------------------------------|------|-------------------|--------------------------------------|--|

| 0    | 0     | 0     | 0     | Normal                                | 0xFF | Immediate         | MAX                                  |  |

| 1    | 0     | 0     | 1     | PWM, Phase<br>Correct                 | 0xFF | TOP               | воттом                               |  |

| 2    | 0     | 1     | 0     | CTC                                   | OCRA | Immediate         | MAX                                  |  |

| 3    | 0     | 1     | - 1   | Fast PWM                              | 0xFF | BOTTOM            | MAX                                  |  |

| 4    | - 1   | 0     | 0     | Reserved                              | -    | -                 | -                                    |  |

| 5    | 1     | 0     | 1     | PWM, Phase<br>Correct                 | OCRA | TOP               | воттом                               |  |

| 6    | 1     | 1     | 0     | Reserved                              | -    | -                 | -                                    |  |

| 7    | - 1   | 1     | 1     | Fast PWM                              | OCRA | BOTTOM            | TOP                                  |  |

Notes: 1 MAY = 0vEE

2 ROTTOM = 0v00

#### 15.9.2 TCCR0B - Timer/Counter Control Register B

| Bit           | 7     | 6     | 5 | 4 | 3     | 2    | 1    | 0    |        |

|---------------|-------|-------|---|---|-------|------|------|------|--------|

| 0x25 (0x45)   | FOCOA | FOCOS | - | - | WGM02 | CS02 | CS01 | C500 | TCCR0B |

| Read/Write    | W     | W     | R | R | RW    | R/W  | R/W  | R/W  |        |

| Initial Value | 0     | 0     | 0 | 0 | 0     | 0    | 0    | 0    |        |

# . Bit 7 - FOC0A: Force Output Compare A

# The FOC0A bit is only active when the WGM bits specify a non-PWM mode.

However, for ensuring compatibility with future devices, this bit must be set to zero when TCCR0B is written when operating in PWM mode. When writing a logical one to the FOC0A bit, an immediate Compare Match is forced on the Waveform Generation unit. The OC0A output is changed according to its COM0A1:0 bits setting. Note that the FOC0A bit is implemented as a strobe. Therefore it is the value present in the COM0A1:0 bits that determines the effect of the forced compare.

A FOC0A strobe will not generate any interrupt, nor will it clear the timer in CTC mode using OCR0A as TOP. The FOC0A bit is always read as zero.

#### . Bit 6 - FOC0B: Force Output Compare B

The FOC0B bit is only active when the WGM bits specify a non-PWM mode.

However, for ensuring compatibility with future devices, this bit must be set to zero when TCCR0B is written when operating in PWM mode. When writing a logical one to the FOC0B bit, an immediate Compare Match is forced on the Waveform Generation unit. The OC0B output is changed according to its COM0B1:0 bits setting. Note that the FOC0B bit is implemented as a strobe. Therefore it is the value present in the COM0B1:0 bits that determines the effect of the forced compare.

A FOC0B strobe will not generate any interrupt, nor will it clear the timer in CTC mode using OCR0B as TOP. The FOC0B bit is always read as zero. These bits are reserved bits in the ATmega48A/PA/88A/PA/168A/PA/328/P and will always read as zero.

#### . Rits 5:4 - Passarvad

Rit 3 – WGM02: Waveform Generation Mode

See the description in the "TCCR0A - Timer/Counter Control Register A" on page 104.

### Rits 2:0 - CS02:0: Clock Select

The three Clock Select bits select the clock source to be used by the Timer/Counter.

Table 15-9. Clock Select Bit Description

| CS02 | CS01 | CS00 | Description                                             |

|------|------|------|---------------------------------------------------------|

| 0    | 0    | 0    | No clock source (Timer/Counter stopped)                 |

| 0    | 0    | - 1  | clk <sub>I/D</sub> /(No prescaling)                     |

| 0    | 1    | 0    | clk <sub>I/O</sub> /8 (From prescaler)                  |

| 0    | 1    | 1    | clk <sub>I/D</sub> /64 (From prescaler)                 |

| 1    | 0    | 0    | clk <sub>I/D</sub> /256 (From prescaler)                |

| 1    | 0    | 1    | clk <sub>I/D</sub> /1024 (From prescaler)               |

| 1    | 1    | 0    | External clock source on T0 pin. Clock on falling edge. |

| 1    | 1    | 1    | External clock source on T0 pin. Clock on rising edge.  |

If external pin modes are used for the Timer/Counter0, transitions on the T0 pin will clock the counter even if the pin is configured as an output. This feature allows software control of the counting.

#### 15.9.3 TCNT0 - Timer/Counter Register

The Timer/Counter Register gives direct access, both for read and write operations, to the Timer/Counter unit ab bit counter. Writing to the TCNT Pegister blocks (memoves) the Compare Match on the following timer clock. Modifying the counter (TCNT0) while the counter is running, introduces a risk of missing a Compare Match between TCNT0 and the OCR0 Registers.

#### 15.9.4 OCR0A - Output Compare Register A

The Output Compare Register A contains an 8-bit value that is continuously compared with the counter value (TCNTD). A match can be used to generate an Output Compare interrupt, or to generate a waveform output on the OCOA on.

#### 15.9.5 OCR0B - Output Compare Register B

The Output Compare Register B contains an 8-bit value that is continuously compared with the counter value (TCNTD). A match can be used to generate an Output Compare interrupt, or to generate a waveform output on the OCOR in:

#### 15.9.6 TIMSK0 - Timer/Counter Interrupt Mask Register

| Bit           | 7 | 6 | 5 | 4 | 3 | 2      | 1      | 0     |        |

|---------------|---|---|---|---|---|--------|--------|-------|--------|

| (0x6E)        | - | - | - | - | - | OCIEOB | OCIE0A | TOIE0 | TIMSKO |

| Read/Write    | R | R | R | R | R | R/W    | R/W    | RW    |        |

| Initial Value | 0 | 0 | 0 | 0 | 0 | 0      | 0      | 0     |        |

# Bits 7:3 – Reserved

These bits are reserved bits in the ATmega48A/PA/88A/PA/168A/PA/328/P and will always read as zero.

# Bit 2 – OCIE0B: Timer/Counter Output Compare Match B Interrupt Enable

When the OCIEOB bit is written to one, and the I-bit in the Status Register is set, the Timer/Counter Compare Match B interrupt is enabled. The corresponding interrupt is executed if a Compare Match in Timer/Counter occurs, i.e., when the OCFOB bit is set in the Timer/Counter Interrupt Flag Register – TIFRO.

# Bit 1 – OCIE0A: Timer/Counter0 Output Compare Match A Interrupt Enable

When the OCIEOA bit is written to one, and the I-bit in the Status Register is set, the Timer/CounterO Compare Match A interrupt is enabled. The corresponding interrupt is executed if a Compare Match in Timer/CounterO occurs, i.e., when the OCFOA bit is set in the Timer/Counter O Interrupt Flag Register – TIFRO.

#### Bit 0 – TOIE0: Timer/Counter0 Overflow Interrupt Enable

When the TOIED bit is written to one, and the I-bit in the Status Register is set, the Timer/Counter0 Overflow interrupt is enabled. The corresponding interrupt is executed if an overflow in Timer/Counter0 occurs, i.e., when the TOV0 bit is set in the Timer/Counter0 interrupt Flag Register – TIFR0.

### 15.9.7 TIFR0 - Timer/Counter 0 Interrupt Flag Register

#### . Bits 7:3 - Reserved

These bits are reserved bits in the ATmega48A/PA/88A/PA/168A/PA/328/P and will always read as zero.

## Bit 2 – OCF0B: Timer/Counter 0 Output Compare B Match Flag

The OCF0B bit is set when a Compare Match occurs between the Timer/Counter and the data in OCR0B— Output Compare Register0 B. OCF0B is cleared by hardware when executing the corresponding interrupt handling vector. Alternatively, OCF0B is cleared by writing a logic one to the flag. When the 1-bit in SREC, OCIE0B (Timer/Counter Compare B Match Interrupt Enable), and OCF0B are set, the Timer/Counter Compare Match Interrupt Enable) and OCF0B are set, the Timer/Counter Compare Match Interrupt is executed.

#### . Bit 1 - OCF0A: Timer/Counter 0 Output Compare A Match Flag

The OCFOA bit is set when a Compare Match occurs between the TimeriCounter0 and the data in OCROA— Output Compare Register0. OCFOA is cleared by hardware when executing the corresponding interrupt handling vector. Alternatively, OCFOA is cleared by writing a logic one to the flag. When the I-bit in SREG, OCIEDA (TimeriCounter0 Compare Match Interrupt Enable), and OCFOA are set, the TimeriCounter0 Compare Match Interrupt is executed.

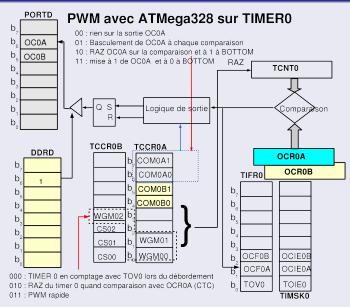

# Synoptique TIMER0